| Product Brief - DPD02 |

Digital Pre-distortion (DPD) has become the industry standard for linearity improvement in digital amplifier designs. By measuring transmitter non linearity and applying an inverse function to the digital modulator output, digital pre-distortion provides automated real time correction of transmitter non-linearities, improving amplifier linearity, efficiency and cost.

The Affarii DPD02 predistortion processor is a third generation adaptive pre-distortion engine providing linearization of RF amplifiers having both reactive and thermal memory characteristics.

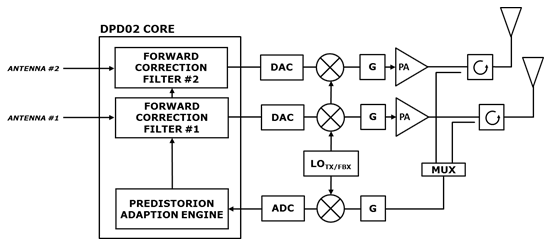

The DPD02 processor includes built-in support for Multi-Output transmitters (MIMO) allowing independent Forward Correction Filters (FCF) for up to four transmit antenna to be slaved to a single master Predistortion Adaption Engine (PAE).

The DPD02 processor is suitable for operation with both Class-AB and Doherty amplifier architectures using industry standard LDMOS and GaN tansistors and provides up to 30dB ofACLR correction in typical designs.

|

|

Figure 1: DPD02 - Multi Antenna Predistortion Block Diagram.

The predistortion processor includes transmit equalization and quadrature modulator correction functions making it is suitable for use with either direct conversion or digital IF transmitter architectures.

Adaption of the filter coefficients is provided by an on chip processor core with hardware acceleration functions. The PAE supporting upto four internal hardware acceleration cores to improve overall MIMO adaption speed and performance.

Figure 2: 20W IMT HPA Multi-cariier WCDMA ("1001") Operation.

The DPD core is suitable for operation with continuous and packet systems and meets the performance requirements of single and multi-carrier 3GPP and HSDPA LTE and WiMAX standards with production margins.

The DPD02 predistortion processor is available as a standalone IP block for Altera and Lattice FPGAs or as part of the digitalTRX solution set.

For further information please contact sales@affarii.com